2026 ATE Load Board 选型终极指南:从引脚数到可靠性评估

核心问题速答:什么是高质量的ATE Load Board?

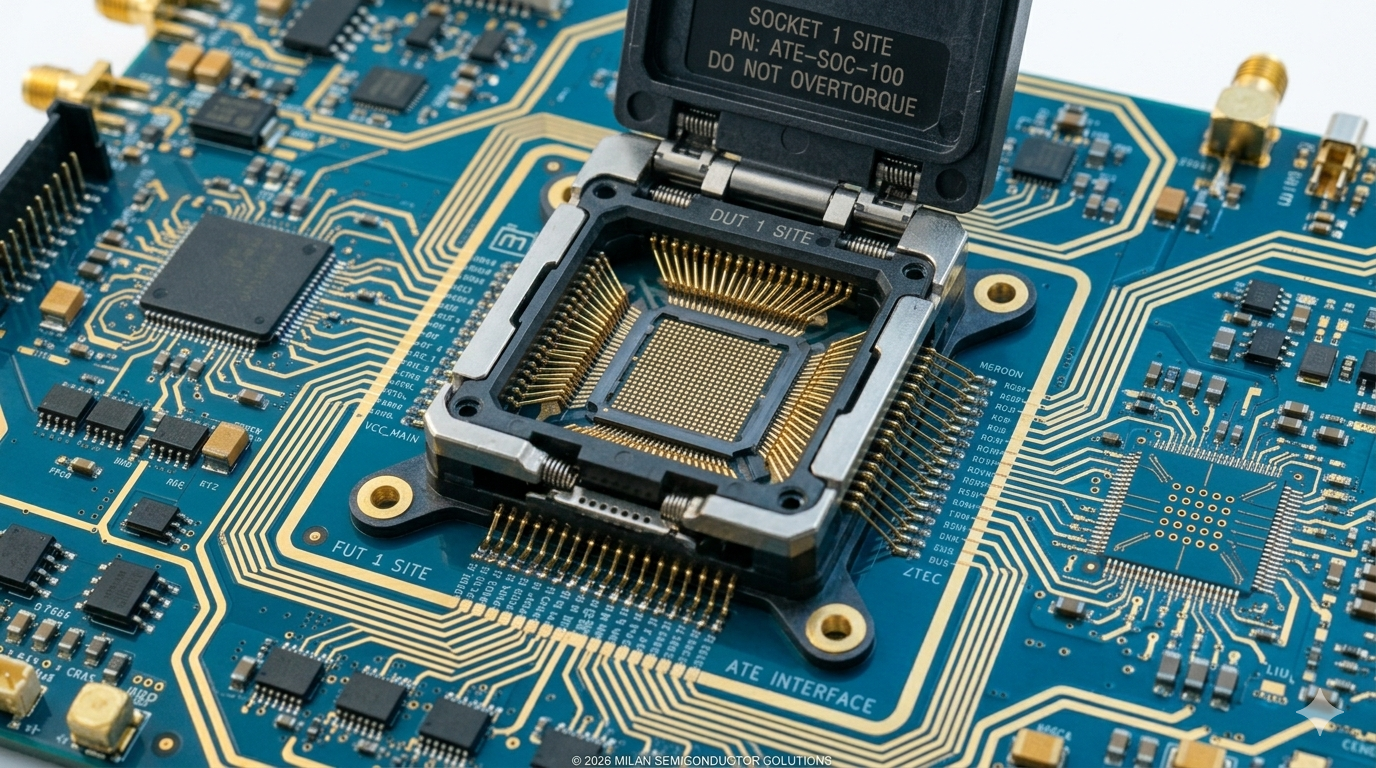

高质量的ATE Load Board是连接测试机(如Teradyne UltraFLEX、Advantest V93000)与待测芯片(DUT)的核心硬件,其核心价值在于精确传输测试信号与电源,确保测试结果的真实性与重复性。

一块优秀的Load Board应具备低损耗信号传输、稳定的电源完整性、精确的阻抗控制以及长期可靠性,最终帮助客户实现更高的首次通过率,并缩短系统启用时间。

引言

在半导体测试领域,ATE Load Board(自动测试设备负载板)是连接测试机台与待测芯片的“最后一厘米”。无论你的测试机是Teradyne UltraFLEX还是Advantest V93000,如果Load Board设计不当,再昂贵的测试系统也无法准确评估芯片的真实性能。

本文将从工程实践角度,为你提供一份全面的Load Board选型指南,涵盖引脚数、信号完整性、电源完整性、热管理、机械结构以及供应商评估六大维度。

1. 引脚数与通道密度:匹配测试机与芯片需求

Load Board的引脚数决定了它能同时测试的芯片数量(并行测试位)以及每个芯片所需的信号通道数。

选型要点:

- 低引脚数芯片:如电源管理芯片(PMIC)、分立器件。可选择标准化的Load Board方案,成本更低。

- 中引脚数芯片:如MCU、混合信号芯片。需要定制化设计,关注信号隔离与串扰控制。

- 高引脚数芯片:如SoC、GPU、AI芯片。需要高层数PCB(≥80层)、微间距布线能力,以及对Teradyne UltraFLEX、UltraFLEXplus或Advantest V93000平台的深度适配经验。

平台适配对比表

| 测试平台 | 典型应用 | Load Board设计要求 | 关键适配要点 |

|---|---|---|---|

| Teradyne UltraFLEX UltraFLEXplus | SoC、GPU、AI芯片 | 高速差分信号、高引脚数、复杂电源网络 | S参数仿真、眼图、 TDR、 热管理 PDN |

| Teradyne J750 | MCU、混合信号 | 中等引脚数、低成本、高并行测试位 | 24通道/板卡、DIB布局优化 |

| Teradyne ETS364/ ETS800,ETS88, ETS88TH | 模拟、功率芯片 | 高电压、大电流、低噪声 | 电源去耦网络、Kelvin连接设计、 隔离设计 |

| Advantest V93000 | SoC、射频、高速数字 | 高频信号、精密阻抗控制 | PS1600/PVIO适配、S参数仿真 |

| Advantest T2000 | 存储、SoC | 高并行度、高吞吐量 | 高速差分总线、时序 |

2. 信号完整性:保证测试数据的真实性

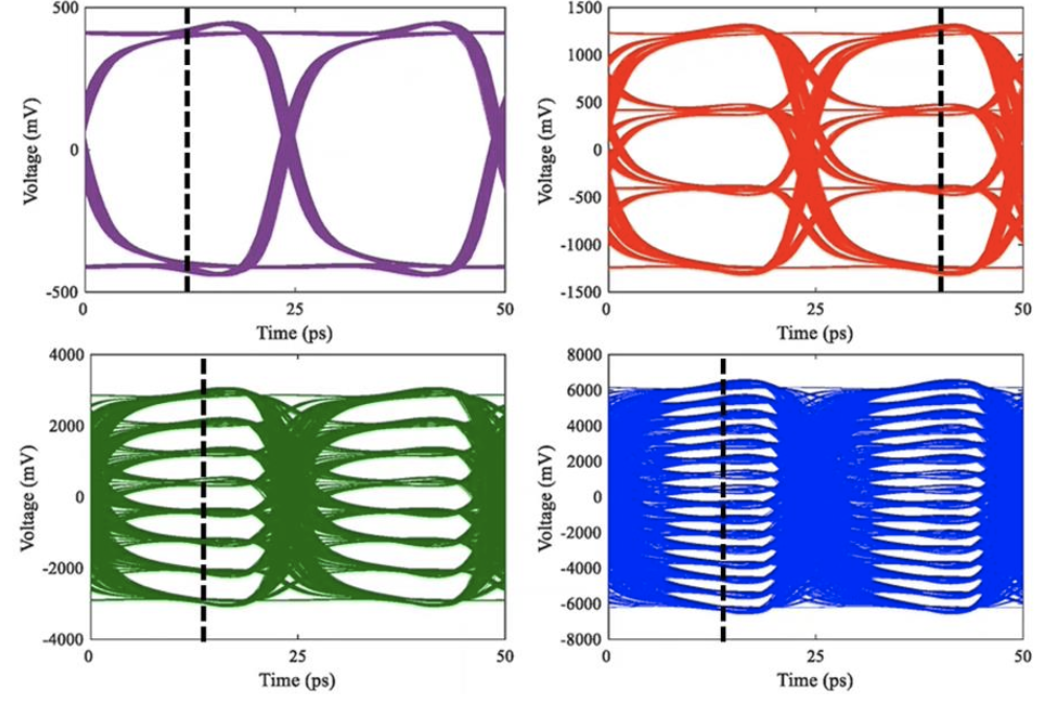

信号完整性是Load Board设计中最核心的技术挑战。在高速测试(>1Gbps)中,任何微小的阻抗不连续都可能导致信号反射、眼图闭合,进而造成测试误判。

关键指标与设计要求:

| 参数 | 推荐值 | 设计要点 |

|---|---|---|

| 特征阻抗 | 50Ω(单端)、100Ω(差分) | 严格控制在±5%以内,通过叠层设计与线宽计算实现 |

| 插入损耗 | -0.5dB/inch @ 10GHz | 使用低损耗材料(如MEGTRON 6、Rogers 4000系列) |

| 回波损耗 | -20dB @ 10GHz | 优化过孔结构、减少stub、使用背钻工艺、优化标贴PAD |

| 串扰 | ≤-40dB @ 10GHz | 增加信号间距、添加地线隔离、使用带状线结构 |

| 眼图高度 | 90% UI | 仿真验证,预留设计裕量、优化S参数,窜扰 |

实践建议:在选型供应商时,要求其提供前仿真(pre-layout)与后仿真(post-layout)报告,并确保其具备矢量网络分析仪进行S参数测试的能力。

3. 电源完整性:为芯片提供“干净”的电力

现代芯片对电源质量的要求越来越高。以AI芯片为例,其核心电压可能低至0.8V,但瞬态电流可达数千安,且要求电压纹波小于±3%。

电源完整性设计要点:

- 低阻抗电源分配网络:通过多层电源平面、适当容值的去耦电容组合,将目标阻抗控制在mΩ级别。

- 去耦电容布局:遵循“从大到小、由远及近”的原则,最小电容(如100nF)应尽可能靠近芯片电源引脚。

- Kelvin连接:对于需要精确电压测量的芯片(如电源管理芯片),应采用四线制Kelvin连接,消除接触电阻和线阻影响。

- 电流承载能力:根据最大电流计算铜厚与线宽,通常使用≥2oz铜厚,必要时增加散热片或风扇。

4. 热管理:应对高功耗芯片的散热挑战

随着芯片功耗不断攀升(AI芯片已达500W以上),热管理已成为Load Board设计中不可忽视的环节。

散热设计选项:

| 散热方式 | 适用功耗 | 设计要点 |

|---|---|---|

| 自然对流 | <10W | 增加铜皮面积、设置散热过孔 |

| 强制风冷 | 10-100W | 加装散热片、优化风道 |

| 液冷 | >100W | 定制水冷板、密封设计 |

| 热电制冷 | 高精度温控需求 | 加装TEC模块、闭环温控 |

可靠性要求:对于汽车电子芯片,Load Board需满足三温测试(-40°C 至 125°C)要求,材料选择需考虑热膨胀系数匹配,避免热循环导致的焊点开裂。

5. 机械结构:加强筋与翘曲度控制

大型Load Board(尺寸>400mm×400mm)在测试过程中可能因自重或温度变化产生翘曲,影响探针接触可靠性。

机械设计要求:

- 加强筋:在板背安装金属加强筋,显著提升刚性。Semiroc提供定制化加强筋解决方案,可根据板形、重量、安装接口进行优化设计。

- 翘曲度控制:行业标准要求翘曲度≤0.1%。通过对称叠层设计、均衡铜分布、适当压合工艺实现。

- 安装接口:确保Load Board与测试机夹具的安装孔位、定位销精准匹配。

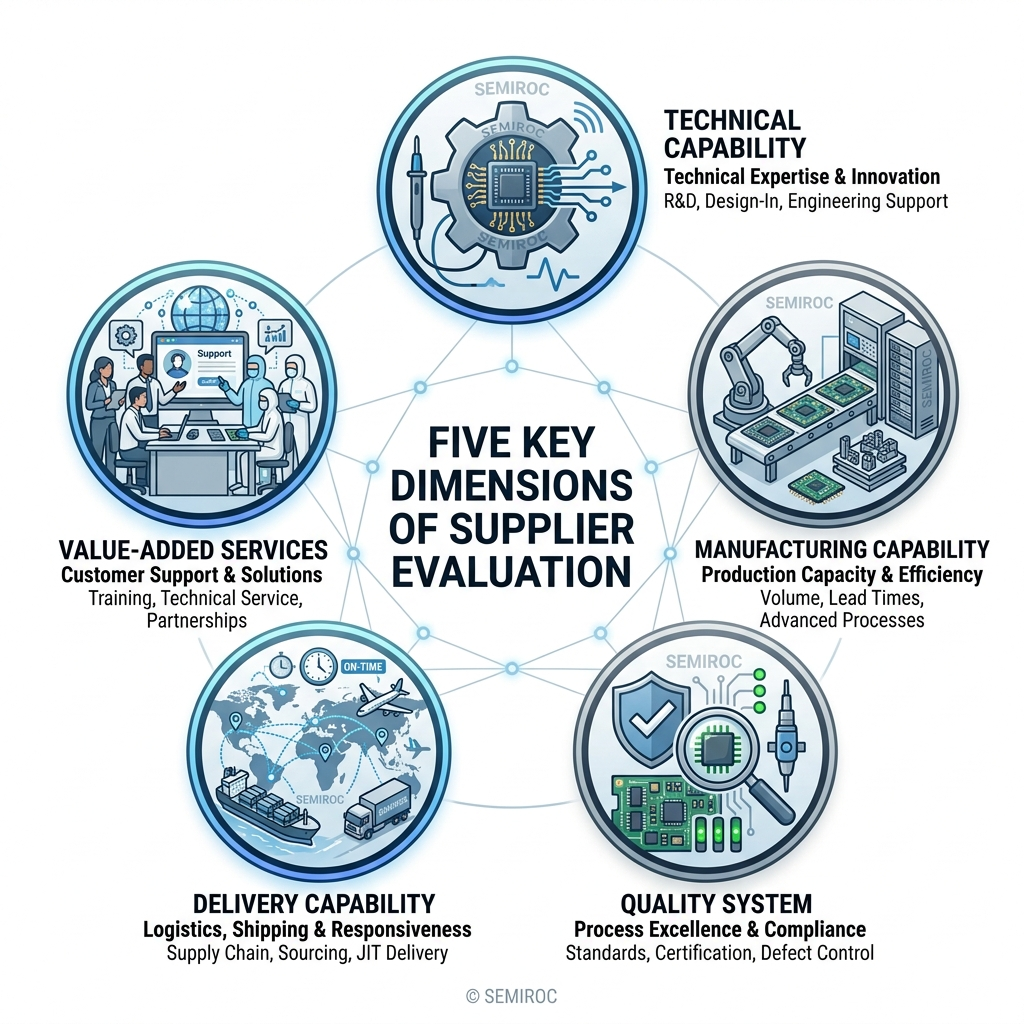

6. 供应商评估:从能力到服务

选择Load Board供应商时,建议从以下维度进行评估:

| 评估维度 | 考察要点 | 理想状态 |

|---|---|---|

| 技术能力 | 仿真工具(SI/PI)、设计经验、平台适配 | 熟悉Teradyne/Advantest平台,有高速、高功率案例 |

| 制造能力 | PCB层数、线宽线距、材料渠道 | ≥70层,2mil线宽,与Rogers等材料商稳定合作 |

| 质量体系 | ISO9001、IATF16949、首次通过率 | FPY ≥85-95%,有完善的质量追溯体系 |

| 交付能力 | 交期承诺、紧急响应 | 标准交期≤3周,可支持紧急项目加急 |

| 增值服务 | 维修翻新、健康监测 | 提供Bin-1服务、在线诊断工具 |

结语

ATE Load Board虽小,却承载着半导体测试的成败。从引脚数到信号完整性,从电源设计到机械结构,每一个细节都可能影响最终测试良率与成本。

作为泰瑞达的战略合作伙伴,Semiroc在Load Board、Probe Card、Cable Assembly等领域拥有深厚积累。我们提供从仿真、设计到制造的一站式Turnkey服务,已助力全球客户实现85-95%的首次通过率,并将系统启用时间缩短20-30%。

联系我们的客服团队解答您的问题!

联系我们