半导体老化测试板设计中的5个常见错误及避免方法

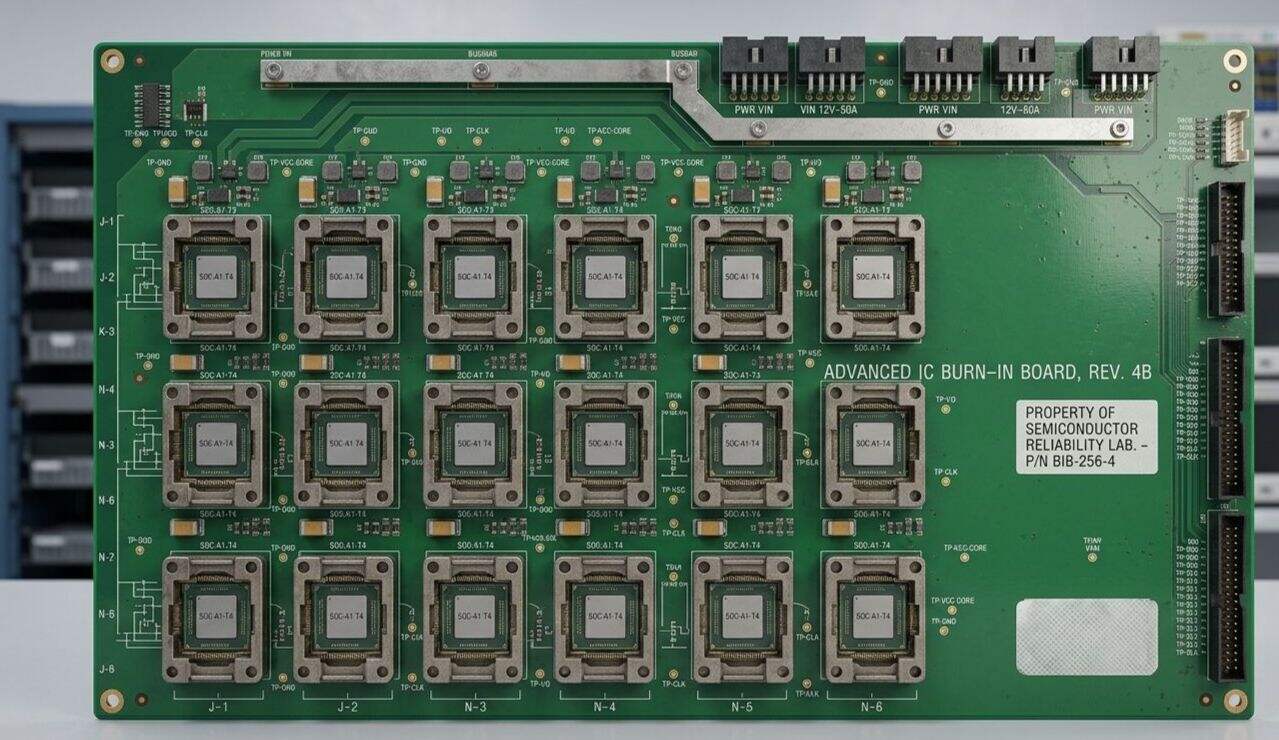

核心问题速答:什么是老化测试板(Burn-in Board)?为什么它容易出问题?老化测试板(Burn-in Board,简称BIB)是用于半导体老化测试的专用接口硬件,通过在高温、高电压、动态信号等应力条件下对芯片进行长时间测试,筛选出早期失效器件。BIB设计的关键难点在于:需要同时兼顾温度均匀性、信号完整性、电源稳定性和长期机械可靠性,任何环节的设计失误都可能导致测试结果失真或硬件过早损坏。

引言

老化测试(Burn-in Test)是半导体可靠性验证的重要手段,尤其对于汽车电子、工业控制、航空航天等对可靠性要求极高的应用领域。老化测试板作为连接老化测试系统(Burn-in System)与待测芯片的核心硬件,其设计质量直接影响测试结果的准确性和测试系统的运行效率。

然而,BIB设计涉及材料科学、热力学、电气工程等多个学科,设计人员常常在以下几个关键环节出现失误。本文将逐一剖析这些常见错误,并提供实用的避免方法。

错误一:忽略温度循环对材料疲劳的影响

问题描述

老化测试通常需要在高温环境下持续运行数小时甚至数天,测试结束后温度降至室温。如此反复的温度循环,会对BIB的材料造成机械疲劳。

许多设计人员在选材时仅关注材料的耐温等级,却忽略了热膨胀系数匹配和抗热疲劳能力这两个同样关键的指标。

常见后果

- PCB层间分离(分层)

- 焊点开裂,导致接触不良

- 插座或连接器的塑料部件老化、脆化

- 探针或弹簧触点的弹力衰减

避免方法

| 设计要点 | 建议做法 |

|---|---|

| PCB材料选择 | 选用高Tg(玻璃化转变温度)材料,Tg值应高于老化测试的最高工作温度。同时关注材料的Z轴热膨胀系数,选择CTE较低的板材 |

| 铜箔与镀层 | 采用延展性较好的铜箔(如Rolled Annealed铜箔),表面镀层推荐使用耐磨、抗氧化的方案(如硬金) |

| 插座选型 | 选择经过温度循环验证的插座产品,关注供应商提供的温度循环寿命数据 |

| 焊点设计 | 对承受机械应力或热应力的元件,可采用底部填充胶(Underfill)加固 |

| 设计余量 | 在温度敏感区域预留应力释放结构,避免刚性固定 |

错误二:电源分配网络阻抗设计不足

问题描述

老化测试中,多颗芯片同时处于工作状态,瞬态电流需求可能远高于常温测试时的水平。如果BIB的电源分配网络(PDN)阻抗设计不当,会导致芯片供电电压波动,影响测试结果的真实性。

常见的问题是:设计人员按照“静态电流”或“平均电流”来设计电源线宽和去耦电容方案,而忽略了瞬态电流对PDN阻抗的要求。

常见后果

- 芯片供电电压跌落,导致被测芯片意外复位或功能异常

- 不同工位之间的电压差异大,测试一致性差

- 电源噪声耦合到信号路径,造成误判

避免方法

| 设计要点 | 建议做法 |

|---|---|

| 电流估算 | 根据芯片规格书中的最大工作电流,并结合老化测试特有的动态测试模式,合理估算峰值电流需求 |

| 电源层设计 | 采用多层电源平面,而非单一线宽。电源平面应尽量完整,避免被信号线割裂 |

| 去耦电容布局 | 采用“大容量电容靠近电源入口、小容量电容靠近芯片电源引脚”的分级布局策略 |

| Kelvin连接 | 对于需要精确电压测量的芯片,采用四线制Kelvin连接,消除接触电阻和线阻带来的测量误差 |

| 仿真验证 | 在投板前进行PDN阻抗仿真,确认目标频段内的阻抗满足要求 |

错误三:信号线长匹配不当导致时序偏差

问题描述

老化测试中,测试系统的驱动信号需要经过BIB到达待测芯片,芯片的输出信号也需要经过BIB回到测试系统。如果不同信号通道之间的传输延迟存在差异,可能导致时序偏差,尤其是在高速接口或并行总线的测试中。

常见问题包括:设计人员未考虑不同信号线之间的长度差异,或未考虑过孔、连接器等结构对延迟的影响。

常见后果

- 建立/保持时间裕量不足,导致数据采样错误

- 多通道并行测试时,不同工位之间的时序不一致

- 高频信号的眼图闭合

避免方法

| 设计要点 | 建议做法 |

|---|---|

| 等长设计 | 对有时序要求的信号组(如数据总线、地址总线),严格控制线长差异 |

| 延迟计算 | 考虑PCB板材的介电常数对信号传播速度的影响,计算实际的传输延迟 |

| 过孔影响 | 过孔会引入额外的延迟和阻抗不连续,应尽量减少关键信号的过孔数量 |

| 连接器差异 | 不同通道在连接器内部的路径长度可能存在差异,选择连接器时关注此项指标 |

| 仿真验证 | 对关键信号进行时序仿真,确认建立/保持时间满足芯片规格要求 |

错误四:插座选型未考虑机械寿命

问题描述

老化测试板在测试过程中需要反复插拔待测芯片,插座的机械寿命直接决定了BIB的使用寿命。许多设计人员在选型时,仅关注插座的电气性能(如接触电阻、带宽),而忽略了机械寿命这一同样重要的指标。

老化测试中,芯片可能需要在高温环境下多次插拔,这对插座的材料和结构提出了更高要求。

常见后果

- 插座在使用一段时间后出现接触不良

- 插拔力变化,导致芯片引脚弯曲或插座损坏

- 频繁更换插座,增加维护成本和测试停机时间

避免方法

| 设计要点 | 建议做法 |

|---|---|

| 寿命数据 | 选型时关注供应商提供的机械寿命数据(通常以插拔次数表示),选择高于预期使用需求的型号 |

| 高温性能 | 确认插座的材料(尤其是塑料部分)在老化测试温度下的性能表现 |

| 接触力设计 | 接触力过大可能损伤芯片引脚,过小可能导致接触不良。选择经过验证的设计方案 |

| 可更换设计 | 对于机械寿命有限的插座,设计时应考虑其可更换性,降低维修难度 |

| 备选方案 | 关键项目可准备备用插座方案,以应对供应链或技术变更 |

错误五:缺乏可维护性设计,维修成本高

问题描述

BIB在使用过程中难免出现故障,常见问题包括插座损坏、连接器接触不良、元件烧毁等。如果设计时未考虑可维护性,维修过程可能非常困难,甚至导致整块BIB报废。

常见问题包括:元件布局过于密集导致难以拆卸、关键测试点未引出、文档缺失等。

常见后果

- 维修时间长,测试产线停机

- 维修过程中损坏周边元件

- 无法准确定位故障位置,整板报废

- 维修成本高,甚至超过新制成本

避免方法

| 设计要点 | 建议做法 |

|---|---|

| 模块化设计 | 将BIB划分为功能模块(如电源模块、信号调理模块、接口模块),便于故障隔离和更换 |

| 测试点预留 | 在关键信号节点预留测试点或测试过孔,便于故障诊断 |

| 元件布局 | 易损元件(如插座、保险丝)应布局在便于操作的位置,周围预留足够的操作空间 |

| 文档完备 | 提供完整的维修手册,包含原理图、元件清单、测试点说明、拆卸步骤等 |

| 维修评估 | 在BIB设计完成后,可由维修工程师评估可维护性,提前发现潜在问题 |

常见错误与避免方法对照表

| 常见错误 | 核心问题 | 避免方法 |

|---|---|---|

| 忽略温度循环对材料疲劳的影响 | 材料选型不当,热膨胀系数不匹配 | 选用高Tg材料,关注CTE匹配,预留应力释放结构 |

| PDN阻抗设计不足 | 低估瞬态电流需求,去耦方案不当 | 合理估算峰值电流,采用多层电源平面,分级去耦 |

| 信号线长匹配不当 | 未考虑传输延迟差异 | 等长设计,过孔优化,时序仿真验证 |

| 插座选型未考虑机械寿命 | 仅关注电气性能,忽略机械寿命 | 关注寿命数据,确认高温性能,设计可更换性 |

| 缺乏可维护性设计 | 布局密集,测试点缺失,文档不全 | 模块化设计,预留测试点,提供维修文档 |

结语

老化测试板的设计是一项系统工程,需要在电气性能、热管理、机械可靠性、可维护性等多个维度之间取得平衡。避免上述五个常见错误,可以显著提升BIB的测试准确性和使用寿命,降低长期运维成本。

作为ATE接口硬件的专业提供商,Semiroc在老化测试板设计领域积累了丰富的经验。我们提供从方案设计、仿真验证到制造交付的全流程服务,帮助客户规避设计风险,加速产品上市。

联系我们的客服团队解答您的问题!

联系我们