2026先进封装测试趋势:为什么ATE接口硬件需要定制化

核心洞察: 2026年,先进封装市场正处于关键的转折点,市场规模预计将达478.8亿美元。在AI与高性能计算(HPC)的驱动下,封装正从芯片的“外壳”演变为系统构建的核心方法论。这一变革对ATE接口硬件提出了前所未有的定制化挑战。

引言

2026年,先进封装已不再是半导体制造的后道工序,而是定义系统性能的核心竞争力。根据Mordor Intelligence最新数据,先进封装市场预计突破478.8亿美元。随着AI算力需求持续膨胀、HBM4进入量产、玻璃基板与面板级封装走向产业化,测试接口硬件正面临根本性的范式转变。

传统的标准化ATE接口已无法满足2026年的测试需求。本文将从五大战略趋势出发,解析先进封装对测试接口硬件的最新挑战,并提供应对策略。

2026年先进封装五大战略趋势及其测试挑战

趋势一:共封装光学(CPO)走向主流

技术背景:

2026年,CPO技术加速商业化,将光学引擎直接集成在封装边缘。这一方案预计可将网络功耗降低70%,成为超大规模数据中心应对AI网络功耗瓶颈的关键技术。

对ATE接口硬件的测试挑战:

- 光电混合测试:需同时测试高速电信号与光学接口,传统纯电测试接口无法满足

- 高频信号完整性:封装边缘的光学引擎要求测试接口具备极低插入损耗

- 多物理场协同:光、电、热三种物理场的耦合测试,要求探针卡与负载板具备跨域仿真能力

趋势二:HBM4量产推动16层堆叠

技术背景:

2026年,HBM4进入量产阶段,采用16层垂直DRAM堆叠(16-Hi),带宽较HBM3e提升一倍以上,以满足AI模型持续扩展的带宽需求。

对ATE接口硬件的测试挑战:

- 超细间距探针:16层堆叠后,TSV间距进一步缩小,对MEMS探针的精度与寿命提出极限要求

- 超高并行测试:单颗HBM堆叠需测试数千个TSV,要求探针卡支持>1000通道/毫米²的密度

- 热应力控制:16层堆叠导致局部热流密度激增,探针卡需具备热补偿设计,确保高温下的接触稳定性

趋势三:玻璃基板与面板级封装过渡

技术背景:

为突破硅中介层的尺寸限制,2026年业界加速向玻璃基板与面板级封装过渡。玻璃基板因其优异的平坦度、可调的热膨胀系数(CTE)及更大尺寸支持,成为先进封装的关键材料。

对ATE接口硬件的测试挑战:

- CTE匹配设计:玻璃基板的CTE与硅芯片更接近,但与PCB差异显著,负载板需采用CTE梯度过渡设计

- 大尺寸翘曲控制:面板级封装尺寸可达600mm×600mm,测试接口需采用多点支撑与加强筋结构,确保翘曲度

- 全新测试接触方案:玻璃基板表面特性与有机基板不同,对探针的接触力、材料选择提出新要求

趋势四:热管理技术突破

技术背景:

3D堆叠导致功率密度激增,2026年AI芯片局部热流密度已达200W/cm²。业界正加速向液冷、背侧供电及新型热界面材料转型。

对ATE接口硬件的测试挑战:

- 液冷集成测试:测试接口需预留液冷管路接口,并在三温测试中确保密封性

- 背侧供电测试:部分先进封装采用背面供电技术(BSPDN),测试需同时接触芯片正面(信号)与背面(电源),对探针卡的双面接触能力提出要求

- 热界面材料兼容:测试接口需适配新型TIM材料,避免测试过程中的热阻偏移

趋势五:Chiplet架构向移动端渗透

技术背景:

Chiplet架构正从数据中心向移动端渗透。据TechInsights预测,2026年智能手机芯片(如苹果A20处理器)可能采用Chiplet设计,打破传统PoP封装格局。

对ATE接口硬件的测试挑战:

- 多芯片互连验证:需在最终测试中验证Chiplet间的互连质量(如UCIe 2.0)

- 低功耗测试适配:移动端对测试功耗敏感,需优化测试接口的寄生电容与电感

- 混合信号测试:移动芯片集成了更多射频、模拟功能,要求负载板具备多域信号隔离能力

2026年先进封装测试趋势汇总

| 战略趋势 | 技术关键词 | 对ATE接口硬件的核心挑战 |

|---|---|---|

| 共封装光学 | CPO,光电集成 | 光电混合测试、超高速信号完整性 |

| HBM4量产 | 16层堆叠,TSV | 超细间距探针、超高并行测试 |

| 玻璃基板 | 玻璃基板,面板级封装 | CTE匹配、大尺寸翘曲控制 |

| 热管理突破 | 液冷,背侧供电 | 液冷集成、双面接触测试 |

| 移动端Chiplet | Chiplet,UCIe | 多芯片互连验证、低功耗测试 |

Semiroc如何应对2026年先进封装测试挑战?

作为ATE接口硬件的专业提供商,Semiroc已针对2026年先进封装趋势布局以下解决方案:

| 挑战 | 解决方案 | 技术要点 |

|---|---|---|

| CPO光电混合测试 | 超低损耗高频负载板 | 采用MLO与Rogers材料,降低插入损耗,支持光电协同仿真 |

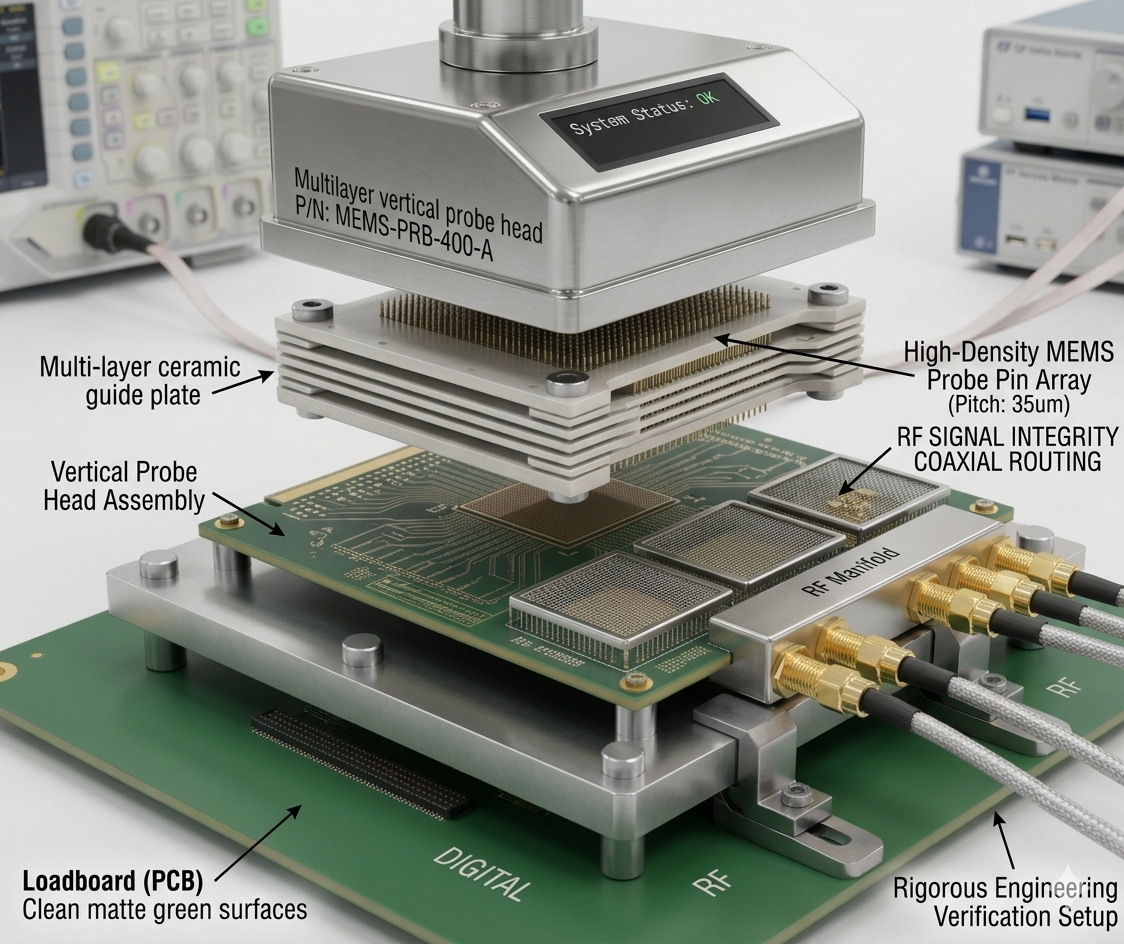

| HBM4 16层堆叠 | 高密度MEMS探针卡 | 更小的间距,接触力精确控制,支持三温测试 |

| 玻璃基板测试 | CTE梯度适配设计 | 多层材料过渡结构,降低翘曲度,支持大尺寸面板 |

| 液冷集成测试 | 集成式热管理接口 | 液冷管路兼容,背侧供电探针卡,TIM适配验证 |

| 移动端Chiplet | 多域信号隔离负载板 | 高速数字/模拟/RF分区设计,支持UCIe 2.0测试 |

未来展望:测试接口将成为先进封装的核心竞争力

2026年,先进封装已从“可选”走向“必选”。共封装光学、HBM4、玻璃基板、液冷集成、移动端Chiplet——这五大趋势共同指向一个方向:测试接口不再是被动的“连接器”,而是与封装设计深度融合的关键环节。

对于半导体制造商而言,选择具备2026年先进封装测试经验的接口供应商,将是确保新产品顺利量产的重要决策。

Semiroc已准备好与您一同应对2026年先进封装的测试挑战。 无论是CPO光电测试、HBM4 16层堆叠、玻璃基板适配,还是千瓦级AI芯片的液冷散热,我们都能提供从仿真到制造的全流程支持。

参考文献

- Mordor Intelligence. (2026). High-End Semiconductor Packaging Market Forecasts 2031.

- TechInsights. (2026). 2026 Advanced Packaging Outlook Report.

- Yole Group. (2026). High-End Performance Packaging 2026.

- IDTechEx. (2026). Thermal Management for Advanced Semiconductor Packaging 2026-2036.

- Teradyne. (2025). UltraFLEX Platform Technical Overview.

联系我们的客服团队解答您的问题!

联系我们